そろそろSRAMについて考えねばと思い、試験回路を作ってみた。

思い返してみると、昔、ひたすらSRAMの回路パターンを見続けていたが、実際に回路を作って動作させてみるのは初めてであった。

思い返してみると、昔、ひたすらSRAMの回路パターンを見続けていたが、実際に回路を作って動作させてみるのは初めてであった。

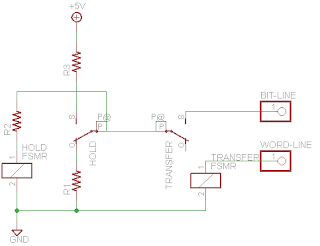

1つのリレーで選択、もう1つのリレーで保持する。CMOSプロセスのSRAMが6Tで実装されているのを考えると2リレーで実装できるのは効率的に見える。これは、W(ライト)時には直接VDDかGNDにつなげて書き換えるのに対し、R(リード)時には160オーム程度のリレーが接続され、保持リレーが影響を受けないのを利用しているためだ。したがって読み取りにバッファが必要と思われる。

bit-lineにリレーをつなげて読み出し中。保持リレーは動作し続けている。

intelがFinFETを使った0.1um2以下のSRAMを動作させている一方で、200mm2以上のセル面積のリレーSRAMに愕然とする。でかい基板でも一枚に4WORD(40bit)しか載らない。アドレス生成を考えなくても、8bit全部使うには2x10x256=5120と天文学的なリレーが必要になってしまう。そもそもアドレスバスは5bitで十分だった気がしてきた。。。

intelがFinFETを使った0.1um2以下のSRAMを動作させている一方で、200mm2以上のセル面積のリレーSRAMに愕然とする。でかい基板でも一枚に4WORD(40bit)しか載らない。アドレス生成を考えなくても、8bit全部使うには2x10x256=5120と天文学的なリレーが必要になってしまう。そもそもアドレスバスは5bitで十分だった気がしてきた。。。

0 件のコメント:

コメントを投稿