CECTPA-1 リレー数まとめ

Data Bus : 10bits

Address Bus : 8bits

Register : 8bits, X/Y

ALU : add, incr, NOP

CLOCK : 2Hz (5clocks per an instruction)

ROM : 11WORDS(110bits)

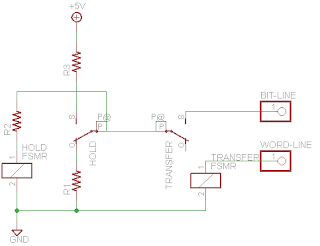

RAM : 3Byte(24bits)

Power : 4e-7MIPS

リレー+ダイオードなら相当楽だと思う。

もしくはCPUはリレーで、メモリは半導体とか(これは他の人も結構やってる)、でもなんか負けた気がする

次回やるとすれば、

・アドレスバスは6bitで十分

・クロックはもう少し早く。今回のシーケンスジェネレータは設計が悪く早められなかった

・各インストラクションに5クロックは4でもよい

・レジスタのLoadはSelectよりタイミング早めてリセットしておくことを忘れない

・基板サイズは大きくする。基板ー基板間のコネクタ・配線に時間をとられるため

・LEDはもっと増やして視覚に訴える。暗い中で実行すると楽しい。

・RAM増やして8x8ディスプレイにマッピングしたい

・簡単なゲーム作りたい、、、が遅すぎるか。