RAMとROMができたのでアドレスデコーダに接続して動作テスト。

上がアドレスデコーダ、真ん中が10WORDのROM、下が1WORDのROM+3byteのRAM。RAMは0x00-0x03に、ROMは0x20-0x29にマッピングされている。

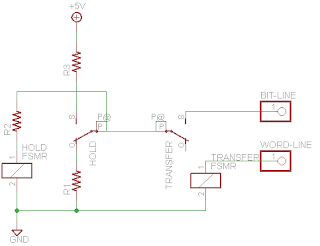

実は設計ミスでアドレスデコーダの配線をやり直してるので、ここまでくるのに結構苦労したのだ。とにかく、メモリはリレーを消費する・・・

それから、eBayでDPDTのリレーを59個調達した。$0.6/DPDTなので激安だと思う。これで10WORD追加できる