ROM1bitにつきリレー一個というのは無駄に思えて、なんとか減らせないかと無い頭を絞って考えたが、結局見つからなかった。抵抗差を利用すれば4bitまでなら抵抗マトリックスだけでも使えそうだが、それでも制御用のリレーを考慮すると得にならない。A/Dコンバータも使えないし・・・。スキャンも考えたが逆に多くなる。おそらく、昔の人もいろいろ考えて結局マトリックスの交点に一素子が使われているのだろうが、その考え方の過程を知りたいぞ。

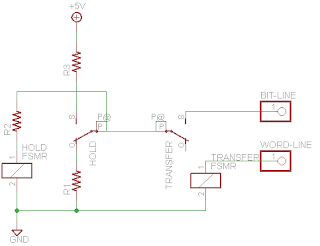

これでは進まないので、1bit1リレーで作り始める。まず回路図。

10WORDS(100bit)のROMボード。裏面の半田付けに心が折れそうになった。。。ラッピングワイヤの半田のノリが悪すぎる。

表側。ぎりぎり入った感じ。

10ワードでは少ないのでリレーが手に入れば追加したいけど大変だからしたくない。