長らく離れていたアマチュア無線だが、コールだけでも取っておこうと、Technician=>General=>Extraと順に受験した。

家から近くHPにまとまっているここが参考になった。

http://www.amateur-radio.org/

最初、walk-inとあってもなにそれ、申請しなくてもいいの?とか、何を用意していけばいいの?と疑問に思うことばかりだった(たぶん、最初に受け方とかも含まれた参考書を買えばよかったんだろうが)。問題がすべてwebにあるので、問題集すら買わなくてもいいかと思った。

問題集

まず、問題は決まっていてその中から出題される。TechnicianとGeneralは300問ずつくらいだし、Technicianは相当簡単なので、同時に受けてもよかった気がする。Generalはバンドプランとか法規覚えることが多く面倒だった。むしろExtraは工学の問題の割合が多く、結構簡単に感じる。

Sunnyvaleの受験場は、公園にある小さい公民館みたいなところで、試験場所を示す看板等は一切ない。Redwoodの受験場は、図書館の2F。住所はWeb上に書いてあるけど、その中のどこかぐらい書いてもいいのでは・・・?とにかく、$15持って、FRNをメモしていけばok。鉛筆や電卓すら貸してくれる。

試験に受かると、VECのページにその日のうちに誰が受験してどのクラスに合格したか表示され、3日するとコールサインが発給される。FCCのHPで住所とかクラスとか確認できる。

FCCのコール検索

1週間以内にARRLからの勧誘と、ライセンスカード(無線従事者+局免許)が届く。なんというレスポンスのよさ、便利さ・・・包括免許があるとは知っていたが、そもそも局免許の概念がないとは。ただし、逆に再申請しないと10年でライセンスが失効する。

カタログ(要するにDM)が届くようになった。ICOM, KENWOOD, YAESU, COMET, DIAMOND ANTENNAと見慣れたメーカーが並んでる。バーテックススタンダードがこっちではYAESUなのか?と思ったら八重洲無線はモトローラに切られていたのね・・・。VX-1で時が止まっていたけど、今はVX-3Rなのかー、ゼネカバ受信と中波コイル付き?これは欲しい。

調べてみたら、日本のリグとコールでそのまま米国で運用できるが、米国のリグ・コールでは日本で開局手続きをしなければならないらしい。この非対称ぷりはなんとかならんか?

JARLの説明

2012年12月16日日曜日

2012年11月25日日曜日

Roomba Controller

部屋の掃除、特にベッドの下の掃除に必要と自分に言い聞かせて、ルンバを買った。

安いタイプでいいと思ったのだが、Fry'sで650がなんと$299で売っていたのでこれに決めた。(さらに掃除交換部品もおまけしてくれた)

amazon最安値でも$399なので大満足。

安いタイプでいいと思ったのだが、Fry'sで650がなんと$299で売っていたのでこれに決めた。(さらに掃除交換部品もおまけしてくれた)

amazon最安値でも$399なので大満足。

Roomba 650。スケジュール機能付き。コイツのおかげで週3回掃除できる。

さて、みんなやってることだろうけど・・・

上蓋を開ける。

sparkfunのBluetoothユニットを購入。作ったのはルンバの電源16Vを5VにしてBluetoothユニットに供給するところだけ。mini DIN 8pinで接続。ルンバのI/Fは公開されていて、115200ボーのシリアル(ただしレベルはTTL)で接続できる。シリアルをBluetoothで飛ばしてNEXUS(スマホ)でコントロールする。

広いところで、どこまでコントロールできるか試してみたが、見通しなら余裕。(上写真の通路真ん中にいるのがルンバ)むしろルンバがよく見えないからコントロールできない感じ。昔、マイクレルの無線チップを買って試した時は15cmくらいしか飛ばず使えねーと思ったが、Bluetoothすげえ。あと、ルンバって丸っこいからどっち向いてるかわかりずらく、コントロールが難しい。

とりあえず全自動の掃除ではうまく汚れた所に行ってくれない時は、これでコントロールできるから便利ではある。さらにラジコンみたいに走らすとか音鳴らすとか自立走行させるとか妄想は膨らむ。

2012年11月19日月曜日

electronic parts

ベイエリアのパーツ屋(電子部品屋)情報をあまり見かけないし、地元の人に聞いても工作しない人は知らないようなので、ここでまとめておこうと思う。

anchor electronics

2040 Walsh Avenue, Santa Clara

mon-fri 7:30-4:00 sat 10:00-3:00・詳細なパーツ表がWeb上にあるため行かなくても値段・在庫がわかる。紙のパーツ表ももらえる

・抵抗、コンデンサ、ICはカウンターで頼む

・パーツ類はよく整理されてて探しやすい、その分やや高め

・年末行くとカレンダーをくれる

1077 East Arques Avenue Sunnyvale

mon-fri 8:00-9:00 sat 9:00-9:00 sun 9:00-7:00

・電気屋だけどパーツも売ってる、けど高い。工具や測定器等は意外と安い。

・Fry's自体はいくつもあるけど、知る限りここが一番在庫がよい

・日曜日に唯一空いてる

156 S. Milpitas Blvd, Milpitas

mon-fri 8:00-6:00 sat 10:00-3:00

・パーツ量はすごい。受動部品とジャンク品が多い。

・個々のパーツに値段は書いてないので、取り出すときに自分で単価と数をメモする必要がある

・安いっぽい。大量に買う必要があるときはここで探すといいと思う。一方、見つけるのが大変。かつ品揃えが片寄ってる

3500 Ryder St, Santa Clara

mon-fri 8:00-7:00 sat 9:00-5:00

・パーツはそれほど整理されてないしジャンクも混ざってる

・一番活気がある(人が多い)

・ケーブルの在庫が多い

・入り口にある箱にパーツを入れていく。紙と鉛筆が入ってて、箱に入れる時に単価や数をメモする

Jameco

1355 Shoreway Road, Belmont

mon-fri 6:00-5:00

・分厚いパーツ表をもらっておく

・パーツ番号表を渡すと、店の人が取ってきてくれる。客がパーツ棚を歩くことはないからあんまりおもしろくない

・平日しかやってないので趣味の人は行きにくいと思う。自分は会社が近いので昼休みにいけるが。

後は、eBay、Digikeyの通販だろうか。shipping高い、配達が遅い。

黄金コースはExcess=>HSC=>Anchor=>Fry'sだろう(1マイル以内なので)

anchor electronics

2040 Walsh Avenue, Santa Clara

mon-fri 7:30-4:00 sat 10:00-3:00・詳細なパーツ表がWeb上にあるため行かなくても値段・在庫がわかる。紙のパーツ表ももらえる

・抵抗、コンデンサ、ICはカウンターで頼む

・パーツ類はよく整理されてて探しやすい、その分やや高め

・年末行くとカレンダーをくれる

mon-fri 8:00-9:00 sat 9:00-9:00 sun 9:00-7:00

・電気屋だけどパーツも売ってる、けど高い。工具や測定器等は意外と安い。

・Fry's自体はいくつもあるけど、知る限りここが一番在庫がよい

・日曜日に唯一空いてる

mon-fri 8:00-6:00 sat 10:00-3:00

・パーツ量はすごい。受動部品とジャンク品が多い。

・個々のパーツに値段は書いてないので、取り出すときに自分で単価と数をメモする必要がある

・安いっぽい。大量に買う必要があるときはここで探すといいと思う。一方、見つけるのが大変。かつ品揃えが片寄ってる

mon-fri 8:00-7:00 sat 9:00-5:00

・パーツはそれほど整理されてないしジャンクも混ざってる

・一番活気がある(人が多い)

・ケーブルの在庫が多い

・入り口にある箱にパーツを入れていく。紙と鉛筆が入ってて、箱に入れる時に単価や数をメモする

1355 Shoreway Road, Belmont

mon-fri 6:00-5:00

・分厚いパーツ表をもらっておく

・パーツ番号表を渡すと、店の人が取ってきてくれる。客がパーツ棚を歩くことはないからあんまりおもしろくない

・平日しかやってないので趣味の人は行きにくいと思う。自分は会社が近いので昼休みにいけるが。

後は、eBay、Digikeyの通販だろうか。shipping高い、配達が遅い。

黄金コースはExcess=>HSC=>Anchor=>Fry'sだろう(1マイル以内なので)

2012年11月14日水曜日

intel museum

インテル博物館に行ってきた。実は二回目だけど。

どこ行ったとか記すのはこのブログの意図ではないが、ここは特別だろう。

どこ行ったとか記すのはこのブログの意図ではないが、ここは特別だろう。

エントランス。ICの発明者でありインテル創始者のノイスに記念している。

キルビーのICはどう見ても無理やりトランジスタ間を配線で繋いだという感じだが、ノイスのICはすでに完成形であったという点でノイスが発明者だと思う。

4004の実体配線図(?)。トランジスタの部分はチップトランジスタが、抵抗に相当する部分にはチップ抵抗が張り付いている等価回路っぽい。全く同じように作れば動くのかな?2300トランジスタだから、がんばれば・・・。I/O周りはドライバ用でFETのWが長い。F.F.はファジリコさんのサインらしい。

他、1101/1103も飾ってあって個人的には内部の回路に非常に興味があるが、全く展示がないのが残念。

2012年11月5日月曜日

CECTPA-1 まとめ

CECTPA-1 リレー数まとめ

Data Bus : 10bits

Address Bus : 8bits

Register : 8bits, X/Y

ALU : add, incr, NOP

CLOCK : 2Hz (5clocks per an instruction)

ROM : 11WORDS(110bits)

RAM : 3Byte(24bits)

Power : 4e-7MIPS

リレー+ダイオードなら相当楽だと思う。

もしくはCPUはリレーで、メモリは半導体とか(これは他の人も結構やってる)、でもなんか負けた気がする

次回やるとすれば、

・アドレスバスは6bitで十分

・クロックはもう少し早く。今回のシーケンスジェネレータは設計が悪く早められなかった

・各インストラクションに5クロックは4でもよい

・レジスタのLoadはSelectよりタイミング早めてリセットしておくことを忘れない

・基板サイズは大きくする。基板ー基板間のコネクタ・配線に時間をとられるため

・LEDはもっと増やして視覚に訴える。暗い中で実行すると楽しい。

・RAM増やして8x8ディスプレイにマッピングしたい

・簡単なゲーム作りたい、、、が遅すぎるか。

2012年10月29日月曜日

火災

住んでいる所が火事になり、すべてが失われました。

数ヶ月作業していたリレーコンピュータがもう少しのところだったのが非常に悔やまれます。

火元等不明ですが、消防士によると、もちろんリレーコンピュータではなく、電気式のコンロから出火していたようです(ただし、私はその3日前から使っていません・・・)

ラップトップはバックアップを取っていましたが、バックアップも同時に焼けてしまったため復活の見込みはありません。すべての情報をクラウドへ、違う場所にバックアップをとることが大切ということが身にしみてわかりました。

再度、一から作り出す気力は今のところ失われました(そもそも子供の頃から揃えてきた工具とかを0から買い直さないといけないし、回路図の元データや一部の図はないので再設計の必要もあります)。

動作中の動画だけでもどこかにアップロードとしておけばよかったのですが、今では一部の写真と記憶に残っているのみです。唯一残ったのはこのブログのアップロードしていた図や写真だけなので、それだけでも手前のメモではなくブログとしてアップロードしてきた意味はありました。

記憶に残っている、リレーコンピュータの到達地点を列挙すると、

・ROMからのインストラクションのロード、解釈

・ジャンプ命令

・即値(Im=>X/Y)

・ADD(X+Y=>X)

・Incr(X+1 => X)

・mov

・load/store(RAMへの書き込み・読み込み)

までは動作していました。メモリも全bit動作良好でした。後は、ifの分岐命令と、NOPの動作調整・確認で完成だったのですが・・・

自分にとっては生涯で一番部品点数の多いプロジェクトでした。コンピュータ(バス/CPU/メモリ)についての理解も深まりました。どう早く計算させるか、ではなくどう部品点数を減らすか、の観点ですが、非常に勉強にはなりました。いつの日か、やる気がチャージされたときに再開できるよう祈ります。

数ヶ月作業していたリレーコンピュータがもう少しのところだったのが非常に悔やまれます。

火元等不明ですが、消防士によると、もちろんリレーコンピュータではなく、電気式のコンロから出火していたようです(ただし、私はその3日前から使っていません・・・)

ラップトップはバックアップを取っていましたが、バックアップも同時に焼けてしまったため復活の見込みはありません。すべての情報をクラウドへ、違う場所にバックアップをとることが大切ということが身にしみてわかりました。

再度、一から作り出す気力は今のところ失われました(そもそも子供の頃から揃えてきた工具とかを0から買い直さないといけないし、回路図の元データや一部の図はないので再設計の必要もあります)。

動作中の動画だけでもどこかにアップロードとしておけばよかったのですが、今では一部の写真と記憶に残っているのみです。唯一残ったのはこのブログのアップロードしていた図や写真だけなので、それだけでも手前のメモではなくブログとしてアップロードしてきた意味はありました。

記憶に残っている、リレーコンピュータの到達地点を列挙すると、

・ROMからのインストラクションのロード、解釈

・ジャンプ命令

・即値(Im=>X/Y)

・ADD(X+Y=>X)

・Incr(X+1 => X)

・mov

・load/store(RAMへの書き込み・読み込み)

までは動作していました。メモリも全bit動作良好でした。後は、ifの分岐命令と、NOPの動作調整・確認で完成だったのですが・・・

自分にとっては生涯で一番部品点数の多いプロジェクトでした。コンピュータ(バス/CPU/メモリ)についての理解も深まりました。どう早く計算させるか、ではなくどう部品点数を減らすか、の観点ですが、非常に勉強にはなりました。いつの日か、やる気がチャージされたときに再開できるよう祈ります。

2012年9月19日水曜日

Operation Decoder(3)

PC(プログラムカウンタ)のloadPC出力にバッファが抜けてるのを発見。バッファがないと信号が逆流してしまうのだ。

ということで、バッファ追加後、JMP命令の動作を確認。データをオペレーションレジスタに保持し、JMPと解釈し、PCを上書き、次のサイクルではPCに書き込まれたアドレスを読みに行っている。

0x00からJMPさせて、その先でもまたJMPさせて0x00に戻す動作も確認した。いよいよCPUらしくなってきたぞ。

ということで、バッファ追加後、JMP命令の動作を確認。データをオペレーションレジスタに保持し、JMPと解釈し、PCを上書き、次のサイクルではPCに書き込まれたアドレスを読みに行っている。

0x00からJMPさせて、その先でもまたJMPさせて0x00に戻す動作も確認した。いよいよCPUらしくなってきたぞ。

2012年8月20日月曜日

Operation Decoder(2)

オペレーションデコーダのテスト中。なぜかデータ6bit目が1だと回路全体がリセットする問題があり、解決に一昼夜費やした。原因はハンダブリッジでVdd(リレーだからVrrか?)がGNDに落ちてたようだ。配線以前の問題だったか。

機能に関係しないリレーを取り外しテストしている様子。

他にもselROMのタイミングを遅らせる必要があり、ディレイを追加。載せているリレー数が足らなくなってきたので、0検出は別基盤対応とする。

0x01以降はRAMなため、0x00はJMPにしROM領域に飛ばなければならない。データをオペレーションレジスタに読み込み、保持し、JMPと解釈し、PCレジスタを書き換えようとするところまでは動作させた。JMPさせる番地にPCレジスタの値が足されてしまう問題があるようだ。タイミングの問題だと思うが。ここまでで出張前の作業は時間切れ。各部のタイミングを一度きちんと考え直さないといけないようだ・・・

2012年8月19日日曜日

Operation Decoder(1)

オペレーションデコーダの設計図が下記。SPDTのリレー数が足らなくて、できるだけDPDTに置きかえてなんとか足りた。画像大きいので注意。

他のユニットと違って、同じ回路は少なく、ほぼランダム。各リレーに番号を振って配線を管理。しかしどこかで間違うだろうな・・・

基本的に論理だけだが、STATE周りでタイミングもあるので、この回路のテストは大変である。

とりあえず実装した写真。やはり表の見た目重視で同じリレーをまとめてみた。ここらへんの実装・配線はかなり突貫作業となったが、この時点で、今年のMaker Fair World応募は不可能になった。Call for makerにはまだ時間があるが、明日から出張で作業できないためである。というか仕事が忙しすぎてテストしている時間がなかったのだ。うむー、協力を申し出てくれたJingも転職してしまうし。

メモリ設計に時間をとられたのが敗因か。その後のMini Maker Fair in Oaklandか、粘って来年のSan Mateoに応募しようか。とにかくここまで来たら動くものを作るしかない。

出張中、時間があれば、秋葉でSPDTリレーを大量購入しよう。ラッピングワイヤはハンダののり的に今使ってる方がよいし、基盤もDigiKeyのが頑丈でよい。DPDTはこの前eBayで安く買ったし、秋葉でしか買えないパーツが減ってきた・・・というかラッピング周りの品揃えが悪すぎる。

2012年7月26日木曜日

Architecture

とうとう最後のユニットであるオペレーションデコーダにとりかかる。この時点で、全体のアーキテクチャを決めなくてはならない。設計に際して変更あると思うが、現時点での構成は下図のとおり。

ALUは現時点でAdd,Thru, Incrだけだが、追加しても基本的な構成は変わらない。

条件分岐はALUからのCarryと、Xレジスタの0検出だけである。条件分岐で次の命令をスキップするのはアドレスを2個進める方法と、次の命令をNOPに変える方法があると思うが、後者を採用する。

後は、いかに命令セットをアーキテクチャに合わせてリレー数を減らすか、だが、拡張性も考慮してある程度クリーンな設計にしたい。考え中の命令セットは下記のような感じ。

01 [8bit] Im => X

10 [8bit] Im => Y

11 [8bit] JMP (Im => PC)

00 0000 [4bit] NOP

00 0001 [4bit] loadRAM => X

00 0010 [4bit] loadRAM => Y

00 0011 [4bit] store X => RAM

00 0100 0001 if zero skip next

00 0100 0010 if carry skip next

00 1000 0000 mov X => Y

00 1000 0001 add X+Y => X

00 1000 0010 Incr X => X

00 1000 [0011 - 1111] reserved for additional operator

最上位2bitで、Im(即値)かJMPかオペレーションかが判断でき、

もしオペレーションであれば、中位4bitでメモリアクセス系か、ifか、ALUか判断できる。

もしメモリアクセス系であれば、下位4bitで指定したアドレスに直接アクセスできる。逆に言うとRAMのアドレス空間は16byteだが、0x00はJMPなので実質15byte。実際は3byteしか作ってないが。

全部0ならNOPで、実装していないアドレスをアクセスしても安全である。

リレーはうるさいので(寿命の問題もあるし)、HALTとリスタートの割り込みも必要かもしれないがまだ未定。

2012年7月16日月曜日

Memory Unit

RAMとROMができたのでアドレスデコーダに接続して動作テスト。

上がアドレスデコーダ、真ん中が10WORDのROM、下が1WORDのROM+3byteのRAM。RAMは0x00-0x03に、ROMは0x20-0x29にマッピングされている。

実は設計ミスでアドレスデコーダの配線をやり直してるので、ここまでくるのに結構苦労したのだ。とにかく、メモリはリレーを消費する・・・

それから、eBayでDPDTのリレーを59個調達した。$0.6/DPDTなので激安だと思う。これで10WORD追加できる

2012年7月4日水曜日

Address decoder

次はアドレスデコーダである。トーナメント的にリレーを組めばいいのだが、例えば6bitをフルアドレッシングするには1+2+4+8+16+32=63ものリレーが必要になってしまう。そこで、下位3bit(8WORD)を1blockとして、上位3bitでblock enableを指定する。こうするとリレーは(1+2+4)x2=14個ですむ。

回路図には描いていないが、データバスに接続するかどうかのselSのリレーもある。

回路図には描いていないが、データバスに接続するかどうかのselSのリレーもある。

SRAM用にはセンスアンプ(とは名ばかりの単なるリレーコイル入力)と、R/W切り替えのリレーが回路図の下半分。SRAMはまだ構想段階だが。

アドレスデコーダとROMを接続して動作確認中。左が以前作った10WORD ROM、右がアドレスデコーダ。上の8LEDがアドレス、下の10LEDが読み出したデータ。次はこれに接続するRAMを作ることにする。どうやらSRAMは半導体のstaticRAMを意味するっぽい.

この場合リレーなので、RRAMと呼ぶことにする。

2012年7月1日日曜日

ROM

ROM1bitにつきリレー一個というのは無駄に思えて、なんとか減らせないかと無い頭を絞って考えたが、結局見つからなかった。抵抗差を利用すれば4bitまでなら抵抗マトリックスだけでも使えそうだが、それでも制御用のリレーを考慮すると得にならない。A/Dコンバータも使えないし・・・。スキャンも考えたが逆に多くなる。おそらく、昔の人もいろいろ考えて結局マトリックスの交点に一素子が使われているのだろうが、その考え方の過程を知りたいぞ。

これでは進まないので、1bit1リレーで作り始める。まず回路図。

10WORDS(100bit)のROMボード。裏面の半田付けに心が折れそうになった。。。ラッピングワイヤの半田のノリが悪すぎる。

表側。ぎりぎり入った感じ。

10ワードでは少ないのでリレーが手に入れば追加したいけど大変だからしたくない。

2012年6月21日木曜日

more relays

SRAMとアドレスレコーダを考えるとリレーが全然足りないので、覚悟を決めてあるだけ全部買って来た。1回路入り1個50セント、40円くらい。秋月より安い。ただ、入荷の予定はないそうだ。JRCと書いてるがYueging(中国)製らしい。eBayで買える中国製は色が青色なのと、サイズがでかいので実装面積の問題がある。オレンジのリレーはHeavy Dutyっぽくて好きなのだが、概して高価。というわけでやっぱり黒色。

買ってきたリレー。だんだん感覚がおかしくなってきて、200個じゃ少ないとか思ってしまう

今あるリレー数をまとめてみた。既に、結構な数を使ってしまっているなぁ。

まずはROMでインストラクションデコーダやアドレスデコーダを作り、残ったリレーでSRAMを作ろうと思う。ROM用に33/68オームのチップ抵抗を1000個ずつ買ってきた。本当は500個でいいのだが、1000個買う方が逆に安いため。また、実装用にDigikeyで6インチ角の基板を注文中。ちなみに、いろいろ探したが基板は秋葉が安い。6.5x4.5inchで20$が相場っぽいが、秋月なら400円だし。唯一6inch角のがDigikeyで11$だったのでメモリ系はこの基板で統一するつもり。これにDIPスイッチを載せられるだけ載せてROMにする(たぶん40WORD=400bit分くらい)。

最近、これに全力を傾けてるけど大丈夫かオレ?

2012年6月20日水曜日

ROM design

SRAMの1bitのコストが高い(1$?)ので、ROMも併用することを考えている。変数はRAM領域を使い、プログラム本体はROM領域に置くという、組み込みでよく見る構成だ。じゃあ、ROMのbitコストはどうなのだろう?最初、ROMでは1個のスイッチと1個のリレーが必要かと思っていたが、下記回路だとスイッチ1個と抵抗2個で実現できる気がする。間違いでした

左の抵抗分圧+スイッチが1bitセル。右のリレーがセンスアンプで、4V以上でon, 3.5V以下でoffになるよう抵抗の分圧を調整する。

真ん中のリレーはenable。ROMを読み出す前にセンスアンプをリセットするために必要。

このままでは負論理になってしまうのでどっかで反転させる必要あり。

テストしているところ。とりあえず動いている。というわけでROMのbitセルは完全に受動部品で実現できそう。

今日はanchor electronicsで2個1$のリレーを買ってきて互換性をテストしてみた。遅延についてはわからないが、とりあえずメモリとしては互換性に問題はないようだ。

2012年6月19日火曜日

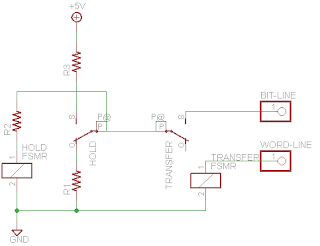

SRAM design

そろそろSRAMについて考えねばと思い、試験回路を作ってみた。

思い返してみると、昔、ひたすらSRAMの回路パターンを見続けていたが、実際に回路を作って動作させてみるのは初めてであった。

思い返してみると、昔、ひたすらSRAMの回路パターンを見続けていたが、実際に回路を作って動作させてみるのは初めてであった。

1つのリレーで選択、もう1つのリレーで保持する。CMOSプロセスのSRAMが6Tで実装されているのを考えると2リレーで実装できるのは効率的に見える。これは、W(ライト)時には直接VDDかGNDにつなげて書き換えるのに対し、R(リード)時には160オーム程度のリレーが接続され、保持リレーが影響を受けないのを利用しているためだ。したがって読み取りにバッファが必要と思われる。

bit-lineにリレーをつなげて読み出し中。保持リレーは動作し続けている。

intelがFinFETを使った0.1um2以下のSRAMを動作させている一方で、200mm2以上のセル面積のリレーSRAMに愕然とする。でかい基板でも一枚に4WORD(40bit)しか載らない。アドレス生成を考えなくても、8bit全部使うには2x10x256=5120と天文学的なリレーが必要になってしまう。そもそもアドレスバスは5bitで十分だった気がしてきた。。。

intelがFinFETを使った0.1um2以下のSRAMを動作させている一方で、200mm2以上のセル面積のリレーSRAMに愕然とする。でかい基板でも一枚に4WORD(40bit)しか載らない。アドレス生成を考えなくても、8bit全部使うには2x10x256=5120と天文学的なリレーが必要になってしまう。そもそもアドレスバスは5bitで十分だった気がしてきた。。。

2012年6月18日月曜日

PC Controller

次はPCのコントローラを作成。ロジックは、

selPC = 1 + 2 + 3

loadPC = 3

selINC = 3 * ^jmp

loadINC = 2

selIncr = 2

数字はシーケンス番号。

これだけだとリレー3個でできるのだが、selをloadより遅延させるため、各selに対し2リレー+CRが必要になる。とりあえずR33オーム、C470uFでPCが正常動作するのを確認。遅延はもっと少なくてもいいかもしれない。

クロック、シーケンスジェネレータ、PCコントローラをつなげてPCを進めているところ。0xFFまで見守って動作を確認。ちなみに0xFFの次は0x00になる。よしよし。

PCが進むだけだが、リレーがガチャガチャ音を立てながら自動で動作しているのは結構おもしろい。

PCが進むだけだが、リレーがガチャガチャ音を立てながら自動で動作しているのは結構おもしろい。

2012年6月15日金曜日

Clock Generator(2)

クロックの問題があったので、後段にFFをつけた。さらに、手動と自動でクロックを切り替えられるようにもした。これはテストの際、便利なはず。

CRの遅延でクロックをつくり、FFで半分の周波数に落としている。もちろん、オシロで見たDutyは1:1だった。

クロック+電源基板の様子。R10オーム、C2000uFの2-3Hzくらいで実験中。左下のプッシュスイッチが手動クロック、その横のトグルスイッチが手動/自動の切り替え。

次はPCまわりのロジックを組んで、PCを進ませてみようと思う。

2012年6月13日水曜日

Sequence Generator

シーケンスジェネレータの回路図。6State目でリセットをかけて初期に戻し、計5つのステートを発生させている。回路図中の100uFがないと、リレー動作中にリセットがかかって発振してしまう。

とりあえずこのユニットは動作するのだが、別の問題が発覚した。リレーの個体差が大きいため、クロックジェネレータが全く発振しなかったり、Dutyが1:1から大きくずれてしまう。CRを最適化した時に使ったリレーはどれかわからず・・・もう少しまともな発振回路を考えねば。

2012年6月10日日曜日

Sequence Generator

Anchor Electronicsでオシロのプローブを買いに行ったのだが、なんと2個で1$の激安5V1回路リレーを発見した。最近、とある人に頼み込み秋月のリレーを買い足したのでしばらく持つが、SRAMを作るときにまた考えよう。

次はシーケンスジェネレータを作ろうと思う。昔Pentiumが出始めた頃、DOS/VマガジンにCPUがどう動作しているかの説明を読んだ記憶がある。1)fetch、2)decode、3)execute、4)storeのシーケンスで一つの命令を実行しているとのことだった。4つのパイプラインを持ってひとつずつずれて実行しているため、見た目1クロックで1命令実行されている。今回考えているCPUは、動作的にaccumulator型なので、データ読み込みとALUの演算をシリアルで行う、つまり1)fetch、2)decode、3)move、4)execute、5)storeの5ステートを発生させる、これがシーケンスジェネレータである。5クロックで1命令、クロックは5Hzなので1命令1秒と遅いが、まぁ速度上げたければクロック上げればいいのだ。

同時に、アドレスバスを使ってPCをインクリメントする、これは3ステップで完了する。SRAM書き込みを考えると5ステートで足りないが、SRAMの見通しが立ってないので後で考えることにする。

回路はone-hot state counterで、5ステート目の次に1ステートに戻るよう、リングにするかリセットする予定。

さて、このプロセッサは半導体を使わず、プリミティブなデバイスのみを使って構成すると決めた。気づいたのだが、このプロセッサは基本的に電位に対して対称である。つまり、電源の±を逆にしても完全に動作するはずである。動作確認用のLEDは光らないが。。。とにかく、真空管コンピュータでもECLでもCMOSでも不可能で、これはすごいアドバンテージではないか。唯一極性があるのは電解コンデンサだが、この優位性を示すため、無極性電解で構成しようと思う。

次はシーケンスジェネレータを作ろうと思う。昔Pentiumが出始めた頃、DOS/VマガジンにCPUがどう動作しているかの説明を読んだ記憶がある。1)fetch、2)decode、3)execute、4)storeのシーケンスで一つの命令を実行しているとのことだった。4つのパイプラインを持ってひとつずつずれて実行しているため、見た目1クロックで1命令実行されている。今回考えているCPUは、動作的にaccumulator型なので、データ読み込みとALUの演算をシリアルで行う、つまり1)fetch、2)decode、3)move、4)execute、5)storeの5ステートを発生させる、これがシーケンスジェネレータである。5クロックで1命令、クロックは5Hzなので1命令1秒と遅いが、まぁ速度上げたければクロック上げればいいのだ。

同時に、アドレスバスを使ってPCをインクリメントする、これは3ステップで完了する。SRAM書き込みを考えると5ステートで足りないが、SRAMの見通しが立ってないので後で考えることにする。

回路はone-hot state counterで、5ステート目の次に1ステートに戻るよう、リングにするかリセットする予定。

さて、このプロセッサは半導体を使わず、プリミティブなデバイスのみを使って構成すると決めた。気づいたのだが、このプロセッサは基本的に電位に対して対称である。つまり、電源の±を逆にしても完全に動作するはずである。動作確認用のLEDは光らないが。。。とにかく、真空管コンピュータでもECLでもCMOSでも不可能で、これはすごいアドバンテージではないか。唯一極性があるのは電解コンデンサだが、この優位性を示すため、無極性電解で構成しようと思う。

2012年6月9日土曜日

Program Counter(2)

PC基板完成。リセットしたときにPCレジスタが0x00になるようにリセットリレーも追加した。ギリギリ入ったが。

気づいたことは、レジスタに書き込む時、ロードを先にオンしてホールドを解いてからセレクトでつなぐ、ロードを先にオフしてホールドしてからセレクトを外す必要がある。デコーダ基板の出力時にセレクトだけ遅延する回路を追加して対応しよう。

動作テスト中、手動でセレクト・ロードしてPCを進めてみた写真。

2012年6月5日火曜日

Program Counter

プログラムカウンタを製作中。右がハーフアダー、真ん中と左がレジスタである。

部品の実装と、ハーフアダーの配線が終わったので、インクリメントのテスト。ハーフアダーの0bit目の繰り上がり入力を常にHにしてやることで、入力に対し常に+1が出力される。動作している!

2012年6月4日月曜日

Program Counter designing

次に作る予定なのは、プログラムカウンタ(PC)である。レジスタ、ALUは組み合わせなので動くが、PCは順序を考えなければならないのでできるか心配である。本質的に、1)次のステップでインクリメントする、2)JMPの時はアドレスを代入できる、の機能を持たなければならない。

いろいろ考えてみたのだが、結局、アドレスを保持するレジスタを2つ持っている必要があると思う。一つ目はPCレジスタそのもので、セレクタ(アドレスバスに接続するスイッチ)を一つ持つ。もう一つはIncrement(アドレスバスの値に+1する)の値を保持するINCレジスタで、これはセレクタを2つ持つ。8ビットの場合、セレクタ1個だけで2回路のリレーを4つ使ってしまうため、セレクタだけで計12個、8bitレジスタは1回路のリレー8個使うので計16個、さらにloadに計2個、Incrementはハーフアダーで1回路のリレー8個+2回路のリレー8個を使うため、PCだけで計46個のリレーを必要とする。ALU基板(44個)よりも多くのリレーを使ってしまうが、これ以上減らすアイデアを考え付かなかった。

実際には8bitフルのアドレッシングなど使わないだろうから、上位ビットのリレーを抜いて再利用すればいいだろうと思い製作にとりかかる。

ブロック図は上記の通り。JMPの際はZレジスタに退避しておいたデータをデータバス経由でアドレスバスにつないで、PCレジスタにロードする。データバスとアドレスバスをつなげるなんて??と思ったが、理屈では合ってるはず。絵ではbranchになっているが、名前はjmpにするべきだったな。

PCのインクリメントは、PCレジスタをアドレスバスに接続するとIncrementが+1してくれるので、それをINCレジスタに保持させ、次のステップでPCレジスタに転送する。うん、想定の中では動きそうだぞ。

2012年6月1日金曜日

Processor Spec.

wire wrap用のピンを使い切ったので、またチマチマwire wrap用ICソケットをばらしてピンを製造中。

ところで、最終形も(頭の中で)固まってきたので仕様をまとめると、

・8bit アドレス

・8bit ALU

・10bit データバス

最小限のCPUを考えた時、4bitだと0-15までしか扱えないのに加え、アドレスが狭くて16行しかコードを書けない。最低限、電卓のようなものをソフトウェアで実装しようとすると、最低でも6bit(64行)は必要と考え、6bitCPUで設計しだしたが、基板の実装のかっこよさから結局8bitCPUにしたのである。

1bitCPU+マイクロコードというのも考えたが、CPU内のステップが多くなるので断念した。

実際、8bitあれば0-255か、負数を考えても二桁の計算はできるし、アドレスも増えて256行まで書ける。まぁ、SRAM1bitに1リレーとしても256*10と、個人としては天文学的なリレー数が必要になってしまうが・・・

考えているインストラクション(10bit、以下1word)

'01' + data(8bit) : data=>X register

'10' + data(8bit) : data=>Y register

'11' + address(8bit) : address=>PC(プログラムカウンタ)、つまりJMP

'00' + instruction(8bit) : 他の命令、例えばaddとか

'00' + '00000000' : NOP SRAMのアドレス範囲外を読んだとき、全部0になるだろうから

他は、計算結果が0なら次の命令をスキップ、Carryで次の命令をスキップを用意すれば、JMPと組み合わせて分岐が組め、最低限の命令セットが揃う。

ネット上で見つけた、似たようなアクティビティは、

MAD研究所のリレー電卓 http://www.fsinet.or.jp/~mad/

回路図はほとんど載ってないが、細かな話が非常に参考になった。

というかリレープロセッサをやろうと思ったきっかけ。SRAMを考えなければ、ワイヤードロジックよりCPU+ソフトウェアの方がリレーを削減できるかもと思った。

Kiの研究部屋のTD4互換リレーCPU http://www.geocities.jp/team_zero_three/index.htm

実は昨日検索して知った。もし作り出す前に気づいたらどうしただろう・・・

ざっと読んでみたが、やはり先駆者はすごい。

レジスタのタイミングが問題になっているようで、非常に参考になる。

とりあえず、他はどうあれ、自分がやりたい、最低限の命令セットで最小限のリレー数で実現するプロセッサを目指すことにする。

6bitの時は、ざっと試算してリレー160個ぐらいで組めそうだった。8bitに変更したが、おそらく2割増程度だろう。ということはリレーたった200個で作れるのか?(SRAMは除いて) 4004のトランジスタ数が2300、8008が3500というからかなり効率的だ。

ところで、最終形も(頭の中で)固まってきたので仕様をまとめると、

・8bit アドレス

・8bit ALU

・10bit データバス

最小限のCPUを考えた時、4bitだと0-15までしか扱えないのに加え、アドレスが狭くて16行しかコードを書けない。最低限、電卓のようなものをソフトウェアで実装しようとすると、最低でも6bit(64行)は必要と考え、6bitCPUで設計しだしたが、基板の実装のかっこよさから結局8bitCPUにしたのである。

1bitCPU+マイクロコードというのも考えたが、CPU内のステップが多くなるので断念した。

実際、8bitあれば0-255か、負数を考えても二桁の計算はできるし、アドレスも増えて256行まで書ける。まぁ、SRAM1bitに1リレーとしても256*10と、個人としては天文学的なリレー数が必要になってしまうが・・・

考えているインストラクション(10bit、以下1word)

'01' + data(8bit) : data=>X register

'10' + data(8bit) : data=>Y register

'11' + address(8bit) : address=>PC(プログラムカウンタ)、つまりJMP

'00' + instruction(8bit) : 他の命令、例えばaddとか

'00' + '00000000' : NOP SRAMのアドレス範囲外を読んだとき、全部0になるだろうから

他は、計算結果が0なら次の命令をスキップ、Carryで次の命令をスキップを用意すれば、JMPと組み合わせて分岐が組め、最低限の命令セットが揃う。

ネット上で見つけた、似たようなアクティビティは、

MAD研究所のリレー電卓 http://www.fsinet.or.jp/~mad/

回路図はほとんど載ってないが、細かな話が非常に参考になった。

というかリレープロセッサをやろうと思ったきっかけ。SRAMを考えなければ、ワイヤードロジックよりCPU+ソフトウェアの方がリレーを削減できるかもと思った。

Kiの研究部屋のTD4互換リレーCPU http://www.geocities.jp/team_zero_three/index.htm

実は昨日検索して知った。もし作り出す前に気づいたらどうしただろう・・・

ざっと読んでみたが、やはり先駆者はすごい。

レジスタのタイミングが問題になっているようで、非常に参考になる。

とりあえず、他はどうあれ、自分がやりたい、最低限の命令セットで最小限のリレー数で実現するプロセッサを目指すことにする。

6bitの時は、ざっと試算してリレー160個ぐらいで組めそうだった。8bitに変更したが、おそらく2割増程度だろう。ということはリレーたった200個で作れるのか?(SRAMは除いて) 4004のトランジスタ数が2300、8008が3500というからかなり効率的だ。

2012年5月31日木曜日

8bit ALU operation

8bit ALU基板の配線完了。思ったほどは配線密度は高くなく、ラッピングなだけに半田付けし直すよりは楽だったと思う。電源の配線し忘れやa接点とb接点の間違いを修正して動くようになった!

動作テスト中。X=1, Y=1の入力で10が出力されてるところ。Add(OUT=X+Y), Inc(OUT=X+1), Thru(OUT=X)の3命令のみに対応。コンセプトとしては最小継電器数で組み上げるモダンCPUということで十分だろう。

2012年5月29日火曜日

8bit ALU

8bit ALUの実装完了、今週は配線に費やされそう。

Add, Inc, Thruの3命令に対応の予定。・・・いまだかつてない実装密度に大興奮だが、裏面の配線はツライ。一個5.5gの継電器だが、42個もあると基板がずっしり重い。

右下のX, Yと書いているところがレジスタからの入力、中央の8x4の継電器群がFull Adder8bit分。

2012年5月27日日曜日

2012年5月26日土曜日

3sets of 6bit register

6bit register 3組、実装完了。

空いているスペースは2bit追加して8bitレジストとしても使えるように残してある。フル実装で24bitレジスタ基盤なのだ。こうしてみると64bitマシンは大変だな。

リレー同士を接触させると、少しの傾きの違いでもずれて見えるので見た目がよくないのはわかっているが、この配置しか考え付かなかった。週末はALUまで仕上げるぞ、という覚悟で就寝

2012年5月24日木曜日

2012年5月22日火曜日

anchor electronics

今日は早起きしてパーツ屋に行ってきた。Fry'sみたいに電化製品+パーツではなく、純粋なパーツ屋である。今まで知らなかった。nVidiaの前にある。

朝7:30からやってるが終わるのが早いし、日曜日はやってないので、仕事に行く前に買いに行く必要がある。

探していたwarp wire用のICソケットを大量購入。

買った袋が左、ニッパで細かくしたのが真ん中、丁寧にプラスチックをとったのが右。

これをリレー用のソケットに使う予定。このピンそのものが売ってればいいのに・・・

ちなみにこの店はラッピング向けの品揃えがよかった。

2012年5月21日月曜日

電源+クロックジェネレータ

とりあえず電源とクロックジェネレータを作成。

電源は後々には強化する必要があるが、そもそも今は秋月の5V3Aアダプタなのでこれくらいで。

クロックジェネレータに空きがあるのは、Dutyに問題があったとき後段にFFつけられるようにするため。

Fry's Sunnyvale店

Fry's sunnyvale店に行った。店内はこんな感じで個包装されたパーツが売っている。秋葉に比べお高め。

というわけでHAKKOのこてを新調した。

登録:

コメント (Atom)